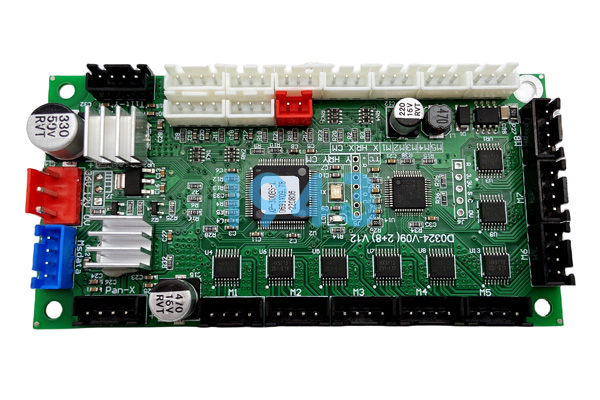

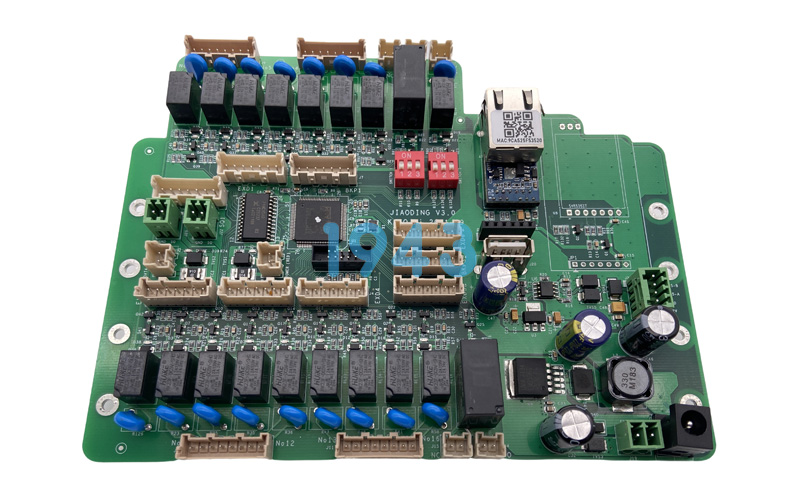

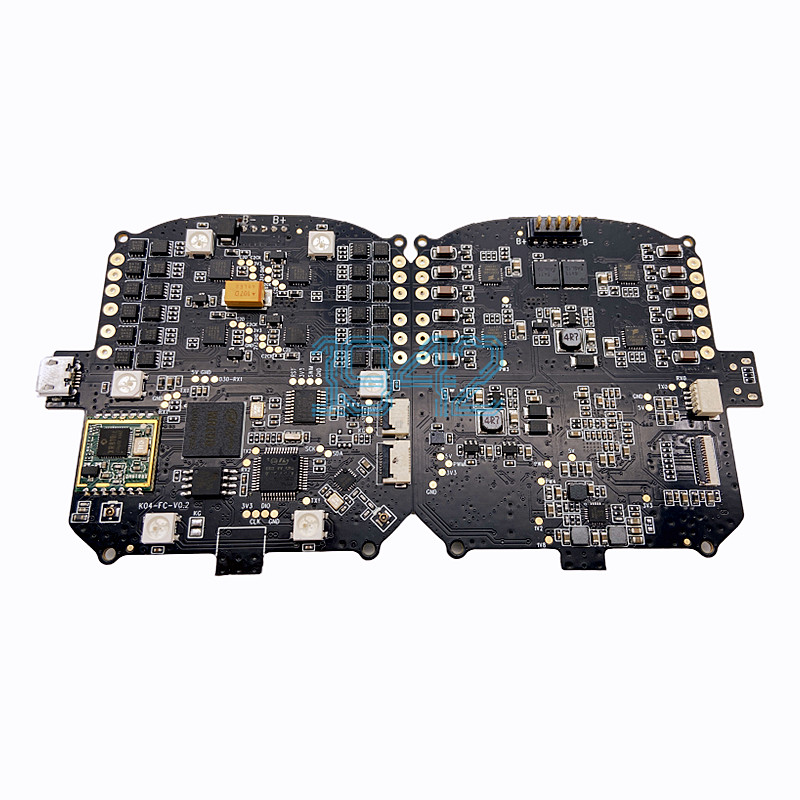

在物联网(IoT)技术迅猛发展的今天,高频高速PCB已成为智能终端、工业互联及5G通信等领域的核心载体。然而,高频信号传输中的衰减、串扰以及电源噪声耦合等问题,正成为制约产品可靠性的关键瓶颈。作为深耕SMT贴片加工领域的1943科技,我们通过系统性技术整合与工艺创新,构建了覆盖设计、材料、制造及测试全流程的信号完整性保障体系,为物联网模块PCBA提供高可靠性的解决方案。

一、高频高速板贴装的信号完整性挑战

物联网模块PCBA的信号完整性面临三大核心挑战:

- 高频信号衰减与串扰:当信号频率超过1GHz时,微带线与带状线的传输损耗显著增加,相邻信号线间距不足易引发串扰,导致数据误码率上升。

- 电源噪声耦合:开关电源产生的谐波噪声可能通过叠层结构耦合至敏感信号线,影响射频模块的相位噪声性能。

- 热应力导致的介电常数偏移:高密度SMT贴片加工中,局部发热可能改变板材介电常数,进而引发阻抗失配。

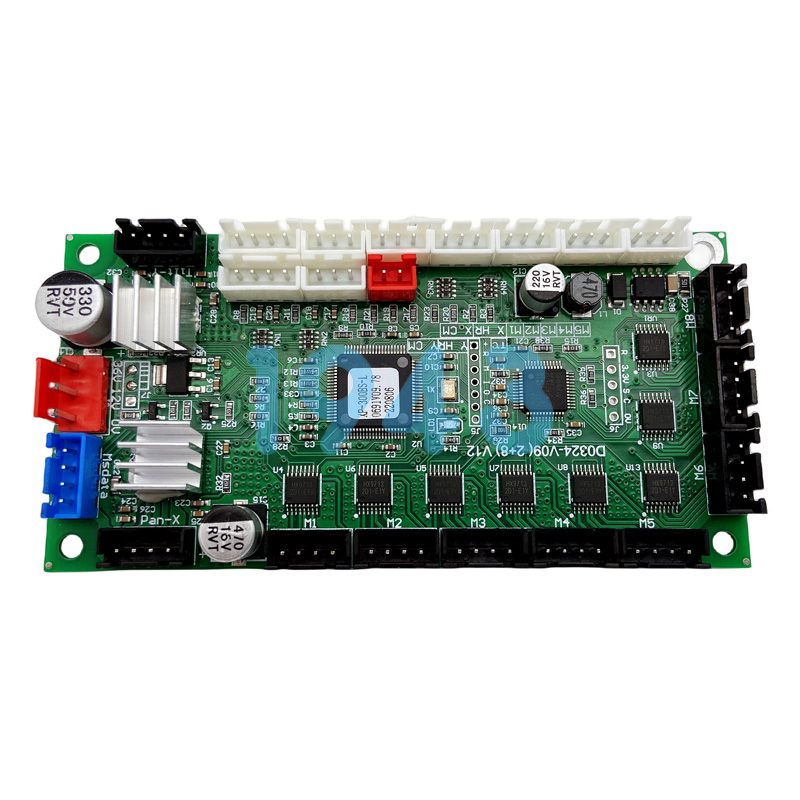

二、叠层设计与阻抗控制的科学优化

1. 对称叠层结构降低翘曲风险

采用偶数层堆叠设计(如6层、8层板),通过“信号层-地层-电源层-信号层”的交替布局,确保板材受热均匀。例如,8层板采用“S-G-P-S-S-P-G-S”结构,可为高速信号提供完整参考平面,同时将电源层与地层间距压缩至0.2mm,增强平面电容效应,抑制高频噪声。

2. 关键信号层内嵌与阻抗匹配

- 高速信号线布局:将DDR、PCIe等关键信号线布置于相邻地层之间,利用地平面屏蔽外部干扰,缩短信号回流路径。

- 微带线与带状线设计:通过调整线宽、铜厚及层间介质厚度,实现50Ω/100Ω标准阻抗的精确控制。例如,带状线设计因电场局限于PCB内层,阻抗控制精度较微带线提升30%以上。

3. 分层供电与去耦电容布局

- 电源层网格分割:将电源层划分为多区域,为不同功能模块独立供电,避免跨区域电流干扰。

- 去耦电容优化:在SMT贴片阶段,将0402封装去耦电容靠近IC电源引脚放置,缩短电流回路,同时采用低ESR钽电容与陶瓷电容组合,覆盖从kHz到GHz的噪声频段。

三、SMT贴片工艺与高频材料的协同创新

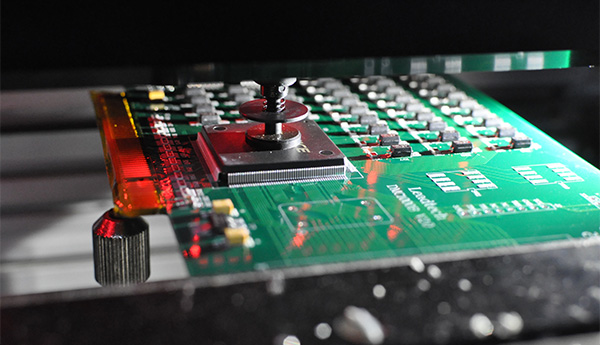

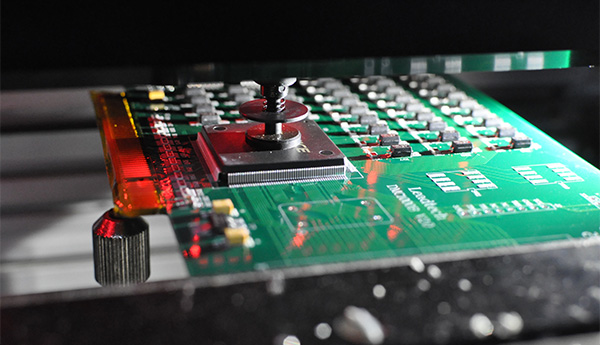

1. 高密度互连(HDI)工艺应用

采用激光盲埋孔技术,减少过孔残桩对高速信号的影响。例如,通过背钻工艺去除过孔短截线,可将10GHz信号的回波损耗从-15dB优化至-25dB。

2. 钢网开口与焊锡量控制

针对BGA、QFN等高密度封装器件,设计阶梯式钢网开口,确保焊锡量均匀分布。例如,0.3mm间距BGA器件采用0.12mm厚钢网,配合回流焊工艺,可将虚焊率降低至0.01%以下。

3. 低损耗基材与表面处理

- 高频基材选择:采用Rogers RO4835等低介电常数(Dk=3.48)、低损耗角正切(Df=0.0037)的板材,减少信号传输损耗。

- 表面粗化处理:通过等离子体蚀刻增加基材表面粗糙度,提升铜箔附着力,避免高频信号传输时的界面反射。

四、信号完整性的测试与验证体系

1. 高频阻抗与插入损耗测试

每块PCBA均进行10GHz、28GHz、56GHz三点阻抗测试,确保差分线阻抗偏差控制在±5%以内。同时,通过矢量网络分析仪测量插入损耗,验证1-110GHz频段内的信号传输性能。

2. 射频性能调试与优化

使用频谱分析仪测试模块的发射功率、接收灵敏度及谐波失真,通过调整匹配网络、校准频率等手段,确保模块在复杂电磁环境下稳定工作。例如,某射频模块经调试后,带外抑制能力提升20dB,满足3GPP标准要求。

3. 环境应力筛选与可靠性验证

模拟高温(85℃)、低温(-40℃)、湿度(85%RH)及振动(5G峰值)等极端条件,进行1000小时连续测试,确保PCBA在恶劣环境下的长期稳定性。测试后阻抗变化率需小于2%,Dk值变化需小于0.03。

五、技术革新:从工艺优化到系统集成

1943科技持续投入研发,推动以下技术突破:

- SiP系统级封装:将射频模块、MEMS传感器及微控制器集成于单一封装,减少互连损耗,提升系统集成度。

- AI驱动的工艺优化:通过机器学习算法分析历史生产数据,预测焊接缺陷风险,实现工艺参数的动态调整。

- 柔性制造系统:基于MES(制造执行系统)与工业物联网技术,实现小批量、多品种订单的快速切换,满足物联网产品迭代需求。

结语

在物联网设备追求“更小、更快、更可靠”的发展趋势下,1943科技以叠层设计优化、SMT工艺创新及全流程测试验证为核心,构建了高频高速板贴装的信号完整性保障体系。我们不仅提供PCBA加工服务,更致力于成为物联网硬件创新的技术伙伴,助力客户在5G、边缘计算及工业4.0等领域抢占先机。

立即联系1943科技,获取定制化高频高速PCBA加工方案,共同开启万物智联的新篇章!

2024-04-26

2024-04-26