在PCBA加工中,电源系统的稳定性直接决定了电子设备的可靠性与性能上限。不少电子工程师在产品研发后期常遇到类似问题:设备运行中频繁死机、高频信号出现杂波干扰、芯片因供电不稳烧毁……这些故障的核心症结,往往指向电源完整性(PowerIntegrity,PI)不足。而电源平面设计的合理性与去耦电容的优化程度,正是影响PI性能的两大关键因素。

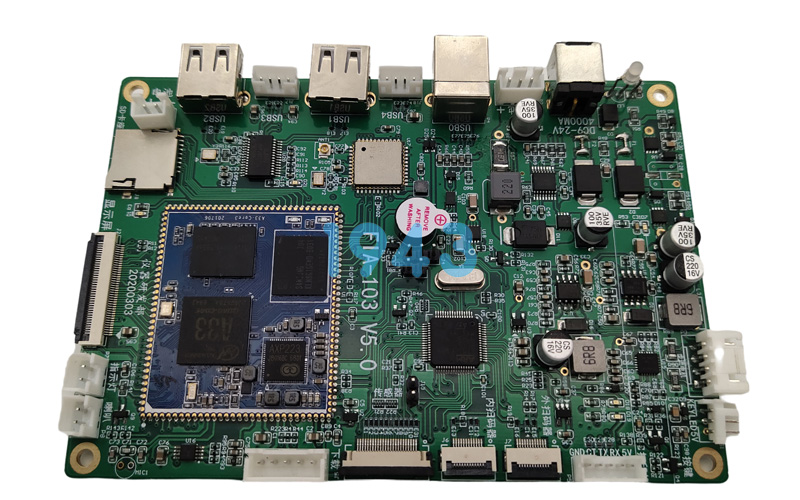

作为专注于高可靠性的PCBA加工服务商,1943科技结合多年行业经验,从技术原理到实操落地,为您拆解PCBA加工中电源完整性分析的核心要点,助力解决供电相关的设计与生产难题。

一、认识PCBA中的电源完整性(PI):为何它是可靠性的基础?

电源完整性(PI)是指PCBA中电源网络(包括电源平面、供电走线、去耦元件等)为芯片提供稳定、低噪声电压的能力。简单来说,就是确保芯片“吃电”稳定——既没有过大的电压波动(如IR压降),也没有高频噪声干扰。

影响PCBA电源完整性的核心因素主要有三类:

- 电源噪声:高频信号切换时产生的电压波动(如同步开关噪声SSN),会干扰芯片正常工作;

- IR压降:电流流经电源平面或走线时,因阻抗产生的电压损耗(即“压降”),导致芯片实际供电电压低于设计值;

- 地弹噪声:地平面电位不稳定引发的噪声,本质是“地-源”压差变化,同样会破坏供电稳定性。

若PI性能不达标,轻则导致设备功能异常(如数据传输错误、传感器精度下降),重则引发芯片烧毁、产品批量返工,直接增加研发与生产成本。因此,在PCBA加工的前期设计阶段,就必须将PI分析纳入核心考量。

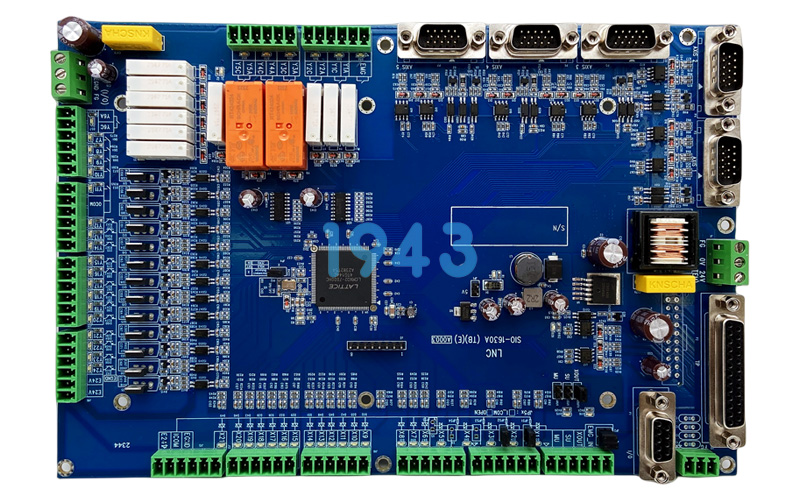

二、PCBA电源平面设计:从“布局”到“阻抗”的全方位管控

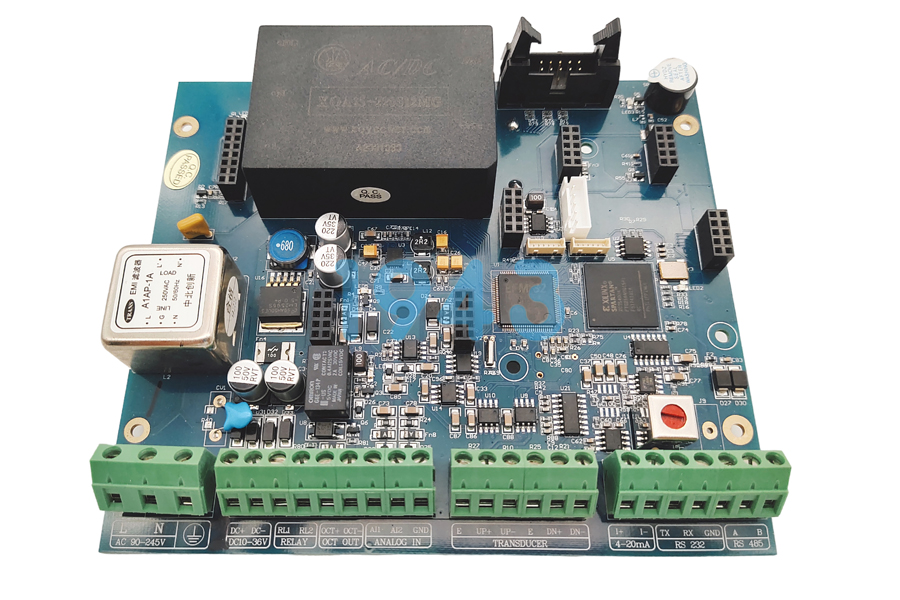

电源平面(而非传统的电源线)是高频、大电流PCBA的主流供电方案,其设计质量直接决定电源网络的阻抗水平与抗干扰能力。1943科技在PCBA加工中,会通过以下三大原则优化电源平面设计:

1.平面布局:优先“地-源对应”,避免不合理分割

- “面对面”叠层设计:电源平面与地平面尽量采用相邻叠层(如“Top-地-电源-Bottom”),形成“电容效应”,降低电源网络寄生电感,同时减少电磁辐射(EMI);

- 避免过度分割:除非有明确的隔离需求(如高低压分区),否则尽量减少电源平面分割——分割会增加电流回路面积,提升阻抗与噪声;若必须分割,分割线需远离敏感信号(如时钟信号、模拟信号)走线,避免交叉干扰;

- 大电流区域单独规划:功率芯片(如MCU、功率管)的供电区域需单独预留足够大的平面面积,避免与小信号电源平面共用,防止大电流波动影响小信号供电。

2.阻抗控制:降低电源网络“内阻”是核心

电源平面的阻抗越低,IR压降与噪声就越小。设计中需重点控制以下参数:

- 铜厚选择:大电流回路(如电源输入、功率模块供电)优先采用1oz以上铜厚(1oz≈35μm),降低走线与平面的直流阻抗;

- 平面尺寸优化:在空间允许的前提下,电源平面面积尽量与地平面匹配,减少电流回路长度——回路越短,寄生电感越小,高频阻抗越低;

- 规避“瓶颈区域”:避免电源平面出现狭窄的“通道”(如宽度<2mm的连接区),防止局部电流密度过高,引发压降增大与发热。

3.抗干扰设计:远离高频信号,减少“耦合噪声”

- 高频信号远离电源平面边缘:高频走线(如USB3.0、PCIe)若靠近电源平面边缘,易与平面产生寄生耦合,引入噪声;建议两者间距≥2mm(或遵循“3W原则”);

- 避免跨分割走线:信号走线不可跨越电源平面的分割线——跨分割会导致信号回路被迫绕行,增加回路面积与噪声,严重时引发信号完整性(SI)问题。

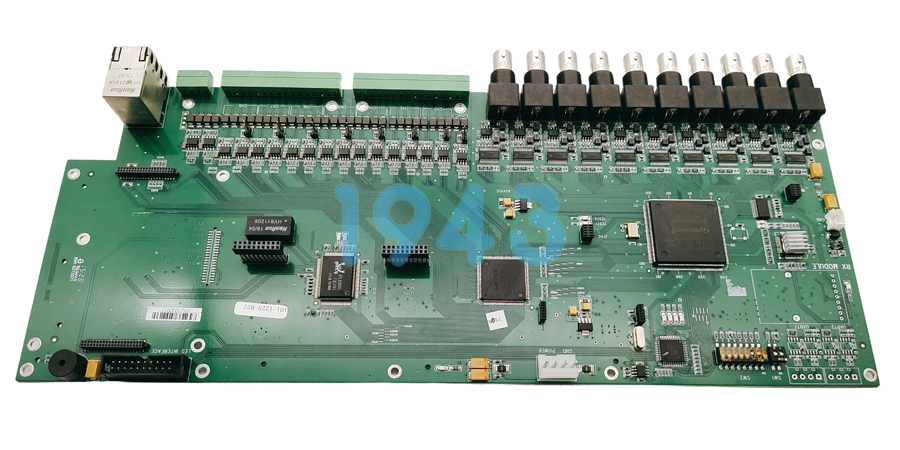

三、去耦电容优化:从“选型”到“布局”的全流程落地

去耦电容是PCBA电源网络的“噪声过滤器”与“应急电源”——既可以抑制高频噪声,又能在芯片瞬时大电流需求时快速补电,是优化PI性能的“低成本高效方案”。1943科技在PCBA加工中,会通过以下四步实现去耦电容的精准优化:

1.明确去耦电容的核心作用

- 高频去耦:抑制100MHz以上高频噪声(如同步开关噪声),通常由小容值电容(如0.1μF、0.01μF)承担;

- 低频储能:应对芯片瞬时大电流(如电机启动、数据突发传输),缓解IR压降,通常由大容值电容(如10μF、100μF)承担;

- 滤波稳压:滤除电源输入中的低频纹波(如线性电源输出的纹波),保障供电baseline稳定。

2.选型:不只看“容值”,更要关注“ESR/ESL”

去耦电容的选型需匹配PCBA的工作频率与芯片需求,核心参数优先级为:ESR(等效串联电阻)>ESL(等效串联电感)>容值:

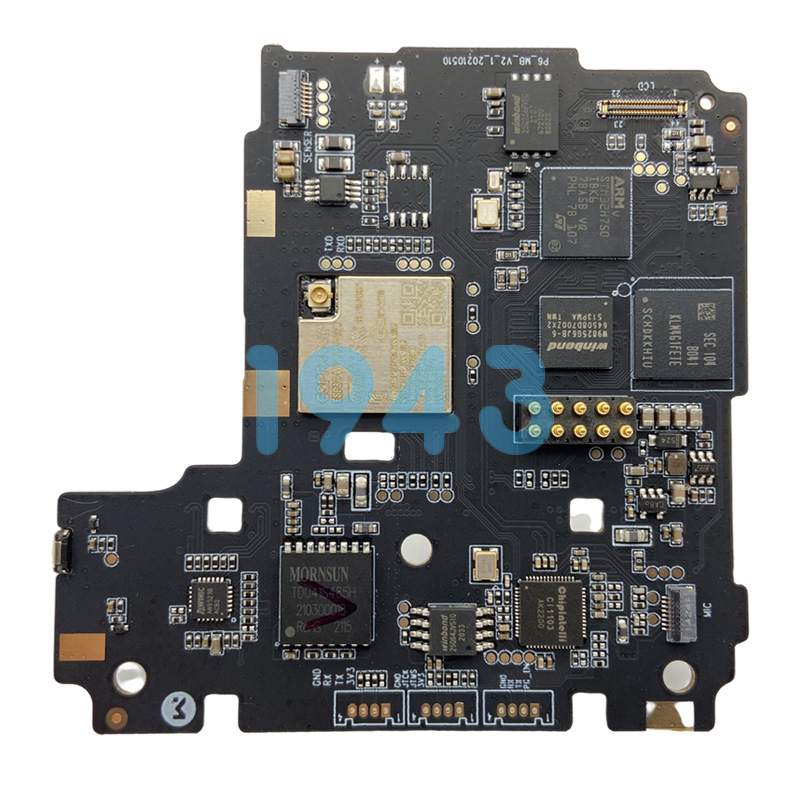

- 容值匹配:高频芯片(如FPGA、射频芯片)建议采用“0.1μF(高频)+10μF(低频)”的组合,覆盖宽频率范围的去耦需求;功率芯片(如DC-DC转换器)需搭配100μF以上的钽电容或铝电解电容,提升储能能力;

- 低ESR/ESL优先:高频场景下,ESR过高会导致去耦电容“失效”(无法抑制高频噪声),建议选择多层陶瓷电容(MLCC),其ESR通常<0.1Ω,远优于钽电容;

- 封装适配:根据PCBA空间与电流需求选择封装(如0402、0603、1206),大电流场景避免使用过小封装(如0402),防止发热烧毁。

3.布局:“靠近引脚+短路径接地”是关键

去耦电容的布局直接影响其去耦效果,错误布局会让“优质电容”沦为“摆设”:

- 紧贴芯片电源引脚:电容与引脚的走线长度需<5mm(越短越好),减少寄生电感——若走线过长,高频噪声会在走线上“损耗”,电容无法有效滤除;

- 接地路径最短:去耦电容的接地端需直接连接到地平面(优先通过过孔直达相邻地平面),避免接地走线绕行,防止形成“大回路”引入噪声;

- 避免扎堆摆放:多个去耦电容不可密集堆叠(间距需≥0.5mm),否则会相互干扰,同时影响散热。

4.数量:“按需配置”,拒绝“越多越好”

去耦电容并非数量越多越好,过度配置会增加PCBA成本与加工难度,需根据芯片功耗与频率计算:

- 参考芯片datasheet:芯片手册通常会明确标注推荐的去耦电容数量与容值(如“每2个电源引脚配置1个0.1μF电容”),需严格遵循;

- 高频芯片适当增加:射频、FPGA等高频芯片,可在核心电源引脚旁额外增加1-2个0.01μF电容,强化高频去耦;

- 避免冗余配置:普通IO口、低速芯片(如单片机),无需过度增加电容,1个0.1μF+1个10μF即可满足需求。

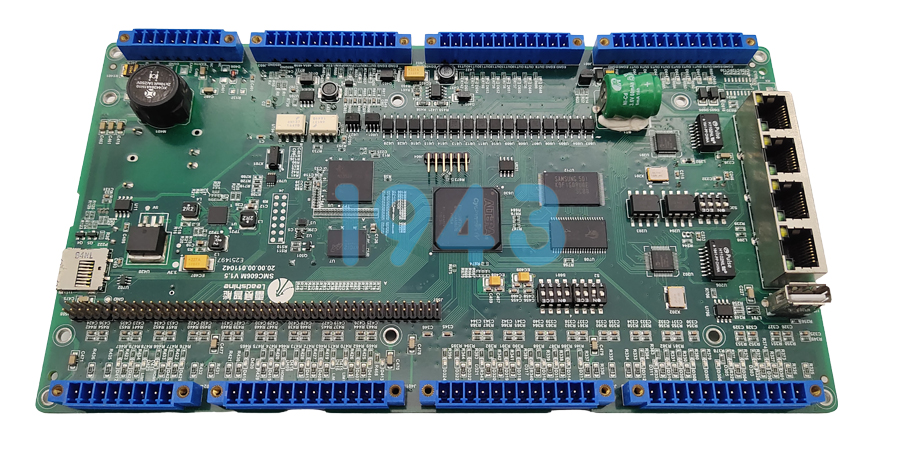

四、1943科技:以PI分析赋能高可靠性PCBA加工

在PCBA加工中,电源完整性分析不是“后期补救”,而是“前期预防”——1943科技将PI分析融入从“设计评审”到“量产交付”的全流程,帮助客户规避供电相关的风险:

- 前期设计评审:针对客户提供的PCB文件,我们的资深硬件工程师会通过专业仿真工具(如Altium Designer PI仿真、ANSYS SIwave),提前排查电源平面分割、去耦电容布局等问题,出具优化建议;

- 样品阶段测试:首件样品生产后,通过阻抗测试仪、示波器等设备,实测电源平面阻抗、电压波动与噪声水平,验证PI性能是否达标;

- 量产过程管控:批量生产中,严格把控去耦电容的物料选型(仅使用符合ROHS标准的MLCC/钽电容)与贴装精度(确保电容与引脚间距<5mm),避免加工误差影响PI性能;

- 定制化解决方案:针对工业控制、汽车电子、医疗设备等对PI要求极高的领域,提供“PI仿真+方案优化+测试验证”的一站式服务,确保PCBA在复杂环境下稳定运行。

结语

电源完整性是PCBA可靠性的基础,而电源平面设计与去耦电容优化,是提升PI性能的“两大抓手”。对于电子企业而言,忽视PI分析不仅会导致产品故障频发,更会增加研发成本与市场风险。

1943科技作为专业SMT贴片加工厂,始终以“技术驱动品质”为核心,凭借成熟的PI分析能力与精细化加工流程,为客户提供高稳定性、高可靠性的PCBA加工服务。若您在PCBA电源设计中遇到难题,或需要免费的PI优化建议,欢迎通过官网咨询入口与我们联系——我们将为您定制专属解决方案,助力产品快速落地!

2024-04-26

2024-04-26