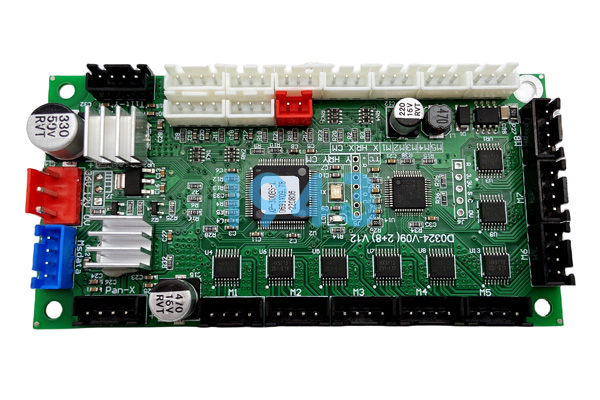

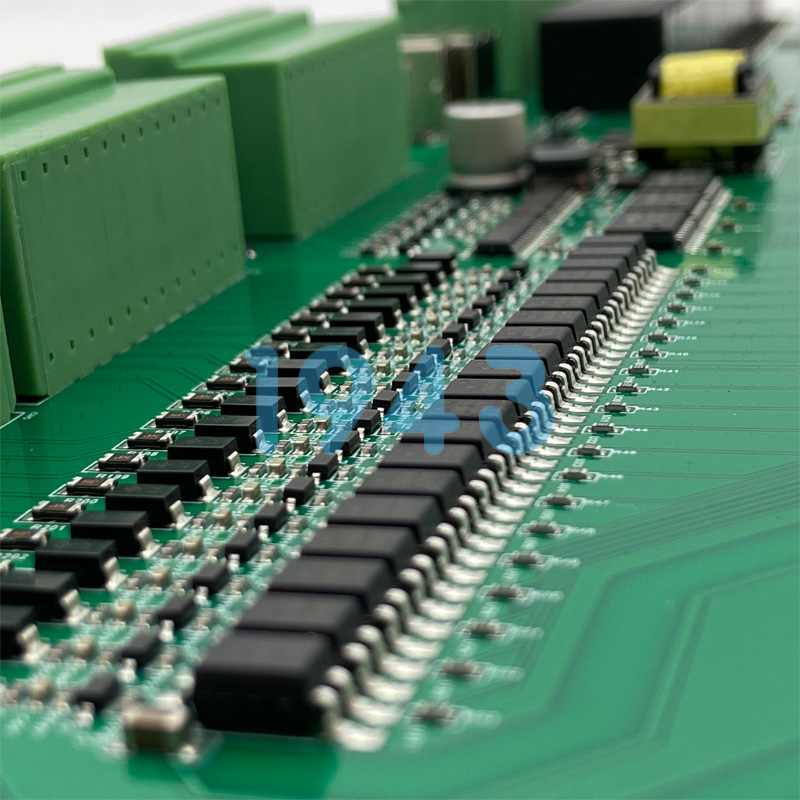

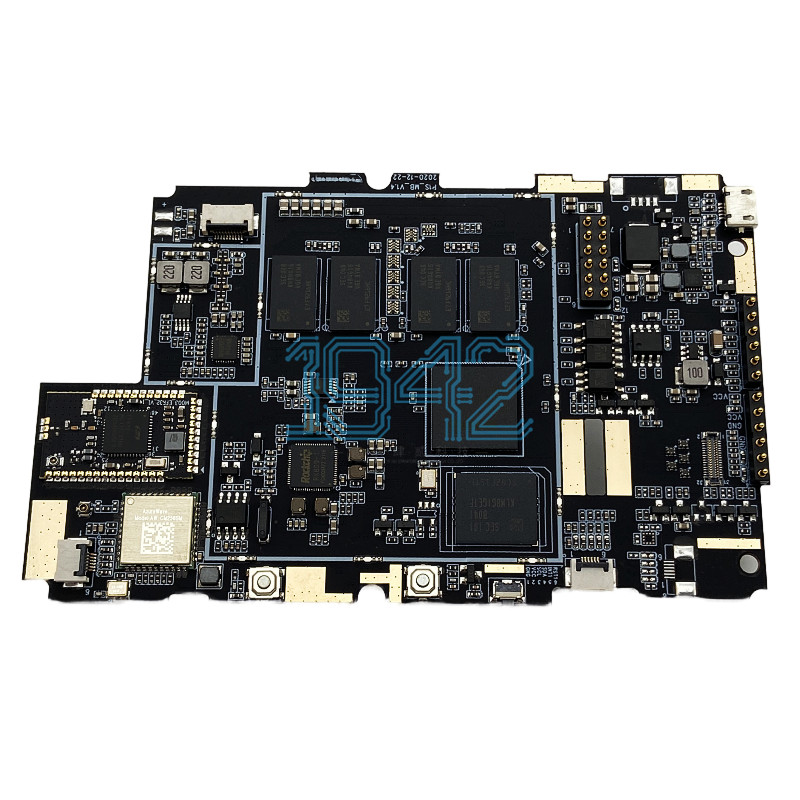

PCBA的电磁兼容(EMC)性能直接决定产品能否通过认证、稳定运行——据行业数据显示,因EMC设计缺陷导致的试产失败率超35%,后期整改成本更是前期设计优化的6-10倍。作为专注SMT贴片加工的1943科技,深知EMC问题对电子企业的影响:小到产品认证受阻,大到市场投诉激增。基于服务工业控制、通讯物联、医疗电子等领域客户的经验,我们总结出“从原理图到布局”的5步PCBA-EMC降噪策略,帮企业从源头规避电磁干扰(EMI)风险,提升产品可靠性。

第一步:原理图阶段——EMC设计的“根基防线”

核心策略:从器件选型到拓扑结构,提前阻断干扰源

EMC设计的关键在“预防”,原理图阶段需重点把控两点:

- 干扰抑制器件精准选型:优先选择自带EMC优化特性的器件——如滤波电容选高频特性好的X7R/X5R陶瓷电容(容值根据频率匹配,100MHz以下推荐0.1μF+10μF组合),功率回路搭配共模电感(额定电流需比实际电流大30%以上),敏感信号端选用ESD保护器件(击穿电压比工作电压高20%);

- 拓扑结构简化与隔离:避免复杂环路(如电源回路环路面积<2cm²),数字电路与模拟电路采用独立供电拓扑,高频信号(>100MHz)单独设计信号链路,减少不同电路间的干扰耦合。

常见误区(忽视原理图EMC)

- 选用普通电解电容替代高频滤波电容,导致100MHz以上干扰无法抑制,产品EMI测试超标;

- 数字与模拟电路共用电源拓扑,模拟信号受数字噪声影响,精度下降30%以上。

1943科技实践建议

我们在接收客户PCBA文件时,会先进行“原理图EMC预审”:通过自制的《EMC器件选型Checklist》校验器件参数(如电容耐压、电感感量),同时用电路仿真工具模拟环路干扰,帮客户在设计初期修正拓扑缺陷——曾有工业控制客户因电源拓扑环路过大导致EMI超标,经原理图优化后,测试通过率从62%提升至98%。

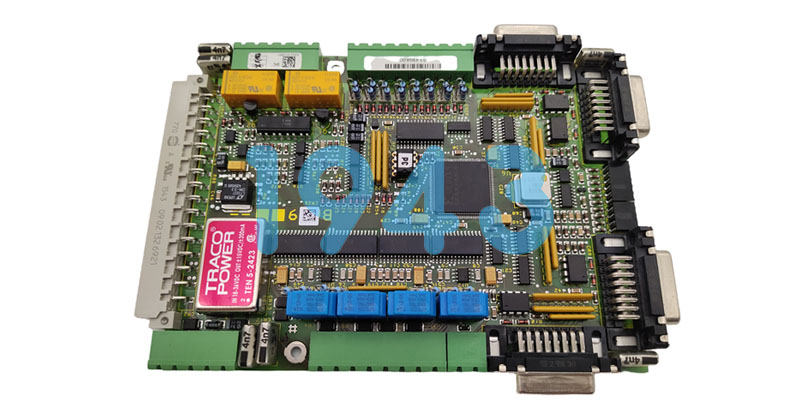

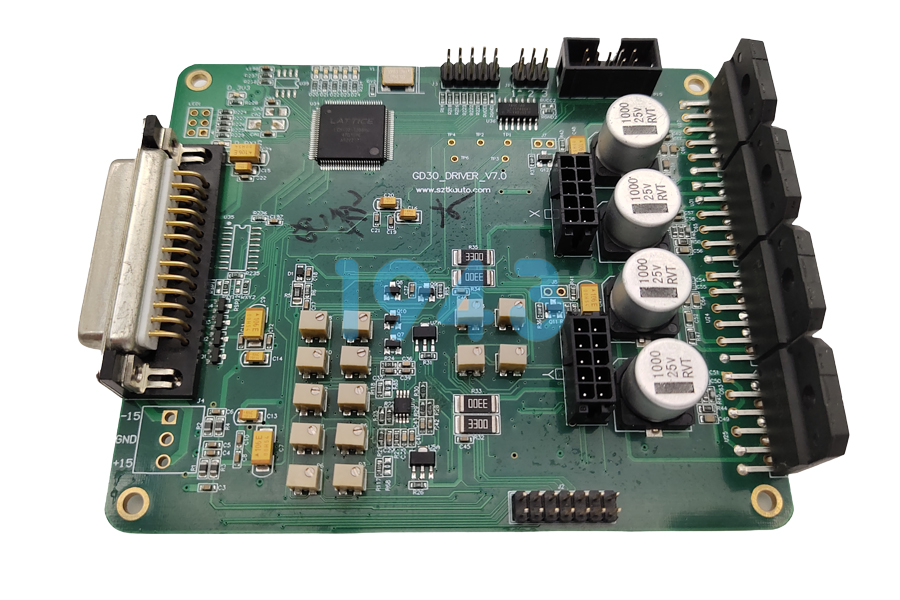

第二步:电源回路降噪——切断EMI“主要传播路径”

核心策略:滤波+接地双管齐下,稳定电源信号

电源是PCBA内部EMI的主要干扰源(占比超40%),需通过“滤波抑制干扰”“接地疏导噪声”实现降噪:

- 多级滤波设计:在电源入口(如DC-DC模块输入端)并联X电容(抑制差模干扰)+共模电感(抑制共模干扰),模块输出端靠近芯片电源引脚处并联0.1μF陶瓷电容(抑制高频噪声)+1μF钽电容(抑制低频纹波),形成“入口-模块-芯片”三级滤波;

- 电源接地优化:采用“单点接地”(数字电源地与模拟电源地在电源入口处单点连接),避免地环路产生;电源滤波电容的接地引脚长度<3mm,减少接地阻抗导致的滤波失效。

常见误区(电源回路设计缺陷)

- 滤波电容远离芯片电源引脚(间距>10mm),高频噪声绕过滤波电容直接进入芯片,导致芯片工作不稳定;

- 数字与模拟电源地多点连接,形成地环路,干扰模拟信号采集。

1943科技实践建议

针对SMT加工中的电源回路可靠性,我们会重点检查“滤波电容布局”:要求电容引脚到芯片电源引脚的走线长度<5mm,且走线宽度≥0.2mm(降低阻抗);对高功率PCBA(如工业电源板),会建议在电源回路增加铜皮面积(≥20mm²),提升散热与抗干扰能力,避免因发热导致滤波器件参数漂移。

第三步:信号路径优化——减少“干扰耦合通道”

核心策略:控制阻抗+隔离走线,降低信号串扰

信号链路的干扰(如串扰、反射)会直接影响PCBA功能,需从“阻抗匹配”“走线隔离”“差分设计”三方面优化:

- 阻抗匹配控制:高速信号(如USB3.0、DDR4)需按特性阻抗设计走线(常见50Ω/90Ω),走线宽度根据PCB叠层(如4层板表层走线宽度0.25mm对应50Ω)调整,避免阻抗突变(如直角走线改为45°角或圆弧走线);

- 敏感信号隔离:低频敏感信号(如传感器输出、ADC输入)与高频信号(如时钟信号、射频信号)的走线间距≥3倍线宽,且避免平行走线(平行长度<10mm),必要时用接地铜皮隔离;

- 差分信号设计:差分对(如HDMI、Ethernet)需等长(长度差<5mm)、等间距(间距为线宽的1-2倍),且远离板边(≥2mm),减少外部干扰耦合。

常见误区(信号路径设计缺陷)

- 高速信号直角走线,导致阻抗突变,反射噪声增加,信号眼图劣化;

- 传感器信号与时钟信号平行走线(长度>20mm),串扰电压超100mV,导致传感器数据失真。

1943科技实践建议

我们的DFM审核团队会用“信号完整性分析工具”校验走线:对高速信号,检查走线阻抗、长度差、过孔数量(单条信号过孔<3个);对敏感信号,标注隔离区域,避免与高频信号交叉;SMT贴装时,会优先贴装敏感信号周边的器件,减少后续焊接对信号链路的干扰。

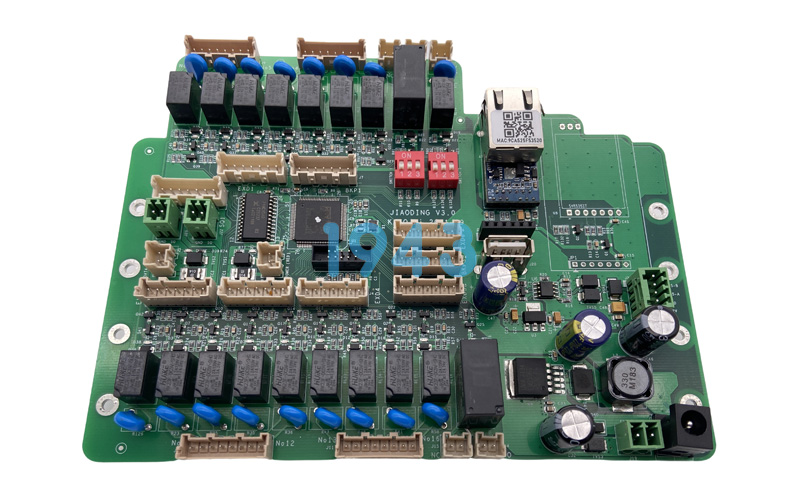

第四步:接地系统设计——构建“噪声疏导网络”

核心策略:分区接地+地平面完整性,避免干扰汇聚

接地不当是EMC问题的“重灾区”,需按“电路类型分区”设计接地系统,确保噪声快速疏导:

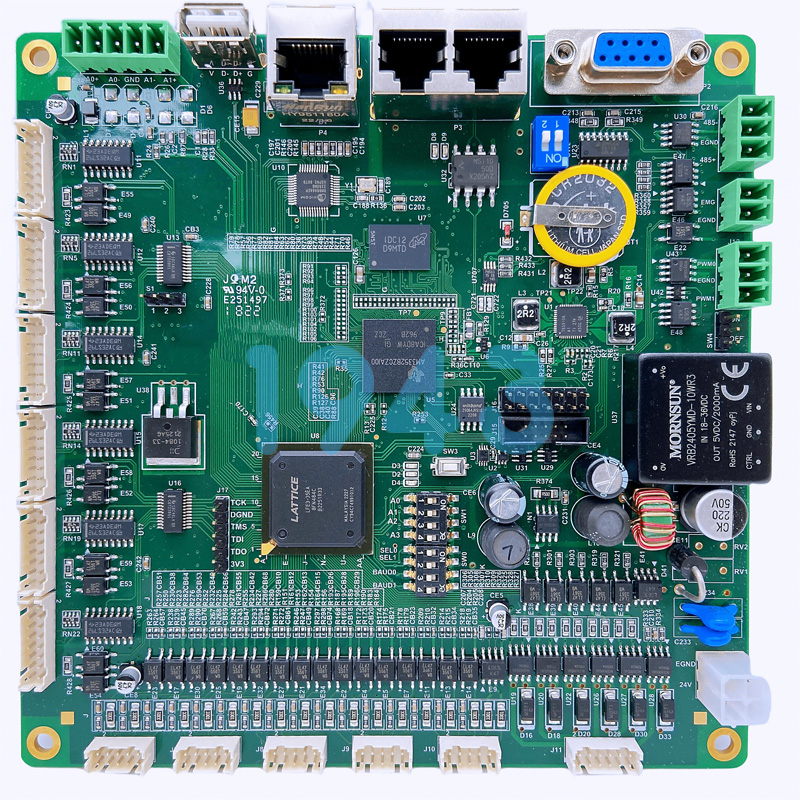

- 接地分区划分:将PCBA接地分为“数字地(DGND)”“模拟地(AGND)”“功率地(PGND)”,各分区通过独立铜皮连接,仅在“接地参考点”(如电源入口处)单点互联,避免跨区干扰;

- 地平面完整性:4层及以上PCB需设计完整地平面(如中间层为地平面),避免地平面分割(如镂空、窄颈),地平面铜皮覆盖率≥70%,提升噪声吸收能力;

- 高频接地优化:高频器件(如晶振、射频模块)的接地引脚需就近连接地平面,且地平面上无过孔(避免干扰泄露),晶振外壳需接地(通过散热焊盘连接地平面)。

常见误区(接地系统设计缺陷)

- 地平面存在窄颈(宽度<1mm),导致接地阻抗增大,噪声无法快速疏导;

- 数字地与模拟地在多个点连接,形成地环路,干扰模拟电路工作。

1943科技实践建议

针对SMT加工后的接地可靠性,我们会检查“地平面连接”:要求各接地分区的连接点采用“星形接地”(单点互联),且连接铜皮宽度≥0.5mm;对高频PCBA(如无线通信板),会建议在晶振下方的地平面增加“接地过孔阵列”(间距1mm),增强噪声屏蔽效果,避免晶振干扰周边器件。

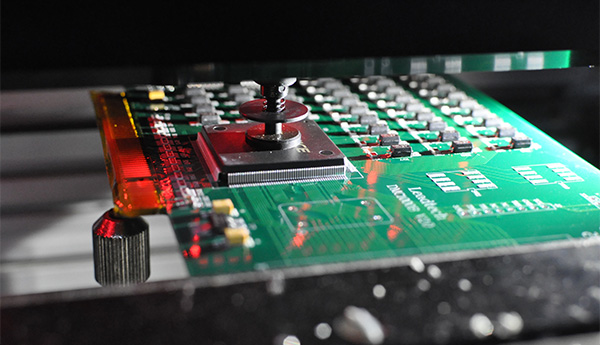

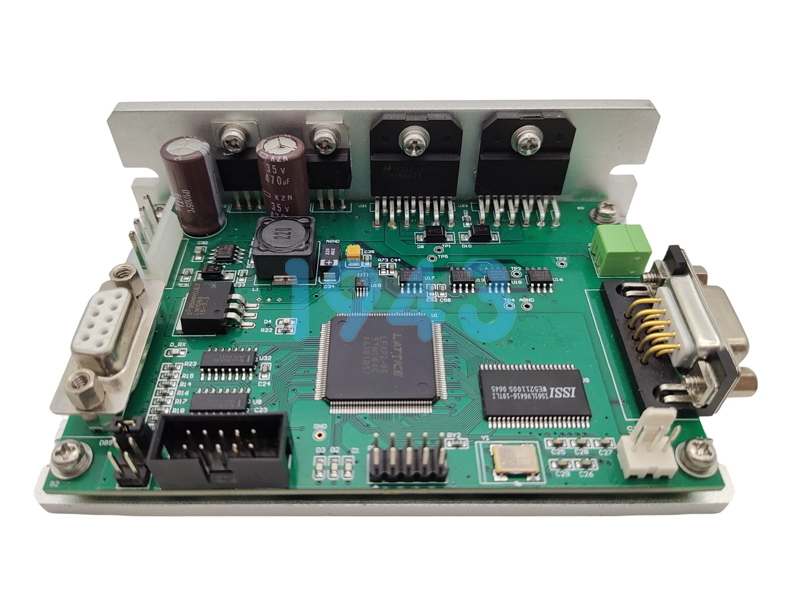

第五步:布局与屏蔽辅助——强化“物理抗干扰屏障”

核心策略:合理布局+屏蔽设计,阻断外部干扰

PCBA布局与屏蔽是EMC设计的“最后防线”,需通过“干扰源与敏感元件分离”“屏蔽结构优化”提升抗干扰能力:

- 布局分区原则:按“干扰源强度”分区布局——高干扰源(如开关电源模块、晶振、功率管)放在PCB边缘,远离敏感元件(如MCU、传感器、ADC),两者间距≥10mm;发热元件(如功率电阻)与EMC器件(如滤波电容)间距≥5mm,避免高温导致器件性能下降;

- 屏蔽罩设计:对高干扰模块(如射频模块、电源模块),采用金属屏蔽罩(厚度≥0.2mm),屏蔽罩底部需有完整接地焊盘(宽度≥0.3mm),且与地平面可靠焊接(SMT贴装时焊锡覆盖率≥90%);

- 接口防护:PCB对外接口(如USB、网口)需靠近板边,且接口处增加ESD保护器件(距离接口引脚<5mm),避免外部静电干扰传入内部电路。

常见误区(布局与屏蔽设计缺陷)

- 开关电源模块与MCU相邻(间距<5mm),MCU受电源噪声干扰,程序运行死机;

- 屏蔽罩接地焊盘不完整,屏蔽罩与地平面接触不良,屏蔽效果下降60%。

1943科技实践建议

在SMT加工前的布局审核中,我们会出具“EMC布局示意图”:标注高干扰源、敏感元件的位置与安全间距;对需屏蔽的模块,设计标准化屏蔽罩焊盘(兼容自动化贴装);贴装屏蔽罩时,采用回流焊工艺(避免手工焊接导致的接地不良),并通过X光检测焊锡质量,确保屏蔽罩接地可靠。

EMC设计是PCBA可靠性的“隐形保障”

对电子制造企业而言,PCBA的EMC性能不仅关系到产品认证通过率,更影响市场口碑与售后成本。1943科技作为SMT贴片加工厂,始终将“EMC设计适配”融入服务全流程——从原理图预审、DFM审核,到SMT贴装、工艺优化,我们以“5步降噪策略”为标准,帮客户规避EMI风险,降低试产返工成本,提升产品竞争力。

如果您的企业正面临PCBA电磁兼容测试失败、干扰导致产品不稳定等问题,欢迎联系1943科技:我们提供免费EMC设计审核服务,结合SMT加工经验,为您定制从原理图到布局的降噪方案,助力产品快速通过认证、顺利量产!

2024-04-26

2024-04-26